|

Embedded System |

|||||||||||

|

CISC vs RISC

CISC stands for Complex Instruction Set Computer and RISC stands for Reduced Instruction Set Computer. This is what all the text book says. Sounds simple ? yes.. but understanding the real meaning would not be simple as it sound. If you see the two words 'ISC (Instruction Set Computer)' is common to both CISC and RISC. If I assume that you know (or vaguely know) what Instruciton Set is, the real difference between CISC and RISC lies in the words 'Complex' and 'Reduced'. What does it by 'Comlex' ? and what does it mean by 'Reduced' ? This is not what you can find easily in text book. Even though they describe on 'Complex' and 'Reduced' in text book, it sounded too dry and abstract, it didn't make much sense to me. The purpose of this page is to help you understand the meaning of 'Complex' and 'Reduced' in my words and I hope this would make more sense to you than textbook.

Before we look into CISC and RISC separately, let's think about the general logic of computations common to any architecture. Step 1 : Read Operands (Value) from memory and move it to specified registers (If the operation needs multiple values, this step can split into multiple sub steps) Step 2 : Apply the specified operation to the values in the registers Step 3 : store the result of the operation to a specified memory location Purely logical point of view, this basic logic applies to both CISC and RISC. However, when we convert this into program (Assembly code, Instruction Set), the resulting instruciton gets different between CISC and RISC. Let's take an example of the simple addition operation 'a = a + b'. The instruction for this operation would be implemented as follows.

Both codes shown above should produce the same result that performes Step 1, 2, 3 described above. However as you see here in CISC only one instruction do the job whereas it requires 4 instructions to do the same job. Now you may feel a little bit strange. 'CISC' implies 'Complex' and 'RISC' sound like 'Simple' because the term RISC is used in contrast with the term CISC. But the program code in CISC obviously look simpler than the code in RISC. This would be confusing (at least it was very confusing to me). This is because the meaning of 'Complex' is not clearly defined. When we say 'Complex', it doesn't mean that CISC is using complex programming sequence to perform a operation. It mean 'One Instruction' in CISC can perform 'Complex functions'. As in this example, in CISC only one instruction 'ADD' perform all the procedures (Step 1, 2, 3) required to achieve a = a + b whereas in RISC four instractuion is required to do the same job. Because of this, the program in CISC system generally requires less amount of program memory. This used to be a great advantage of CISC when the memory was expensive resources in old days. However, memory has not become such a expesive resources any more now. So motivation for CISC has gone much weaker.

Why weaker motivation ? Even though the size of programming memory is not a limitting factor, isn't it still good to use CISC because programming seems to be much simpler ? If you are programming in Assembly, I think CISC programming can be easier (less tedius) than in RISC, but if you are programming in high level language like C / C++, the simplicity in assembly code would not be such an important attraction because it is the compiler's job (not your job) to generate the assembly code.

There is another drawback in CISC. Have you thought of how CISC can perform such a complex job with single instruction ? I am not a CPU designer who can explain this with full experties.. but what I can say is that 'the complex functionality with single instruction' is implemented by hardware (basically more transistors at the bottom). It implies that the logic circuit to execute instructions in CISC tend to be more complicated than the one in RISC.

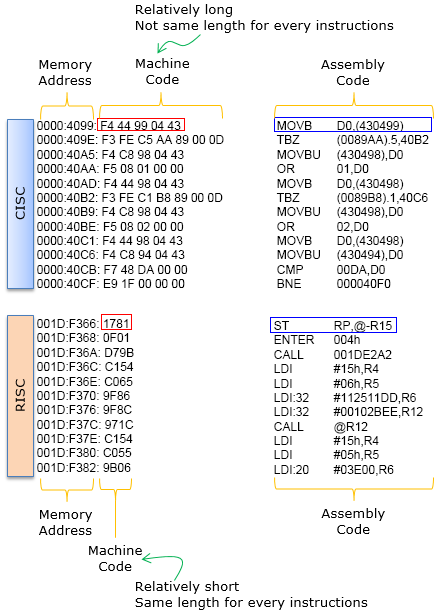

Another fundamental difference between CISC and RISC is depicted below. As you see here, the machine code instruction is relatively long and the length varies depending on instructions in CISC, but in RISC the machine code is relatively short and the length of the instruction is same for all instruction. Longer instruction implies that it may take multiple clock cycle to execute single instruction in CISC. The shorter/simpler instruction implies that it would take only one cycle to execute an instruction in RISC. Actually, RISC is designed in such a way to guarantee to execute single instruction in single cycle. Also, same instruction length for all instruction in RISC implies that every instruction can be executed within the same length of cycle.

There are several other differences between CISC and RISC, but I think most of those additional differences are based on the fundamental differences described above. These differences can be summarized as follows.

Recent Trends

Recently not so many chipset vendors try to differentiate their chipset as pure RISC or pure CISC. General trend is to try to combine the advantage of RISC and CISC, for example, to implement CISC like instructions with simplified hardware. You can easily find a lot of chipset (especially Embedded Microcontroller) claiming that they are using a combined architecture.

Reference :

[1] What is RISC and CISC Architecture with Advantages and Disadvantages [2] RISC vs CISC

|

|||||||||||